به نام خدا!

سلام....

توی این ویدئو با یه چیز جدیدی آشنا شدم وسعی کردم اونو به صورتی که ساده باشه و خودم فهمیدن براتون توضیح بدم!

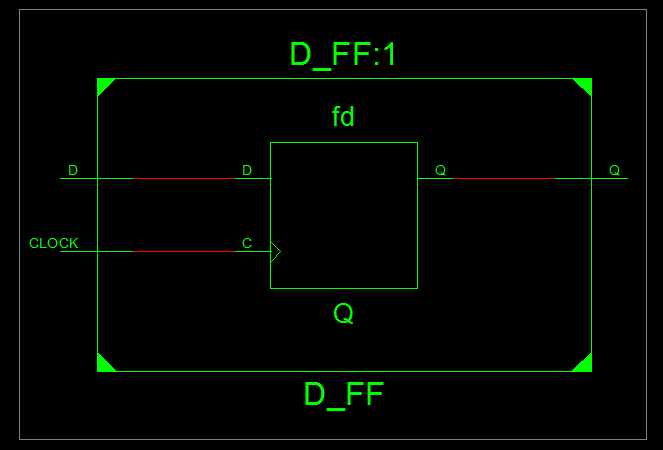

خیلی سادست کسانی که با فلیپ فلاپ آشنایی دارن اصلا دانلود نکن این فیلم برای کسانی هست که دقیقا نمیدونن فرق فلیپ فلاپ ها با همدیگه چیه! (البته توی این فیلم فقط فیلیپ فلاپ نوع d رو بررسی کردم!)

امیدوارم به دردتون بخوره! میتونید از لینک زیر دانلود کنید!

سرور پرشین گیگ ( برای دانلود غیر مسقیم اینجا کلیک کنید)

سرور بیان

اینم آدرس سایتی که توی فیلم معرفی کردم!

اینم کد VHDL البته توی سایت بالا هستش!

library ieee;use ieee. std_logic_1164.all;use ieee. std_logic_arith.all;use ieee. std_logic_unsigned.all;entity D_FF isPORT( D,CLOCK: in std_logic;Q: out std_logic);end D_FF;architecture behavioral of D_FF isbeginprocess(CLOCK)beginif rising_edge (clock) thenQ <= D;end if;end process;end behavioral;

کد زیر هم برای شبیه سازیش!

LIBRARY ieee;USE ieee.std_logic_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--USE ieee.numeric_std.ALL;ENTITY DFF_TB ISEND DFF_TB;ARCHITECTURE behavior OF DFF_TB IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT D_FFPORT(D : IN std_logic;CLOCK : IN std_logic;Q : OUT std_logic);END COMPONENT;--Inputssignal D : std_logic := '0';signal CLOCK : std_logic := '0';--Outputssignal Q : std_logic;-- Clock period definitionsconstant CLOCK_period : time := 10 ns;BEGIN-- Instantiate the Unit Under Test (UUT)uut: D_FF PORT MAP (D => D,CLOCK => CLOCK,Q => Q);-- Clock process definitionsCLOCK_process :processbeginCLOCK <= '0';wait for CLOCK_period/2;CLOCK <= '1';wait for CLOCK_period/2;end process;-- Stimulus processstim_proc: processbegin-- hold reset state for 100 ns.wait for 100 ns;wait for CLOCK_period*10;-- insert stimulus hered <= '1';wait for 10 ns;d <= '0';wait for 3 ns;d <= '1';wait for 50 ns;d <= '0';wait for 100 ns;wait;end process;END;

اینم عکسش توی شماتیک ISE!

یا علی مدد...!